| Version 27 (modified by , 10 years ago) (diff) |

|---|

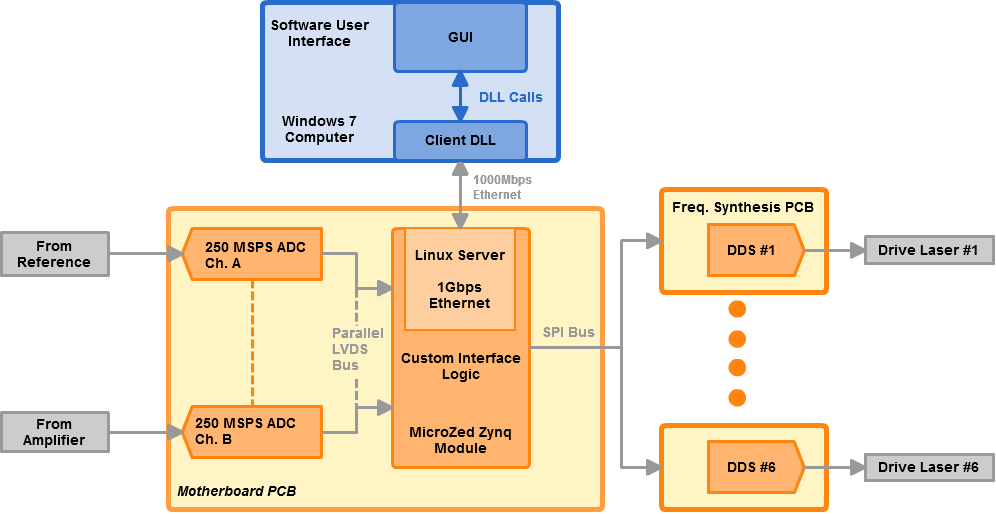

The dDOS (digital diffuse optical spectroscopy) Spectrum Analysis Unit (dSAU) is a device being developed for Professor Darren Roblyer and the Biomedical Optical Technologies Lab (BOTLAB). It will aid in his research in the use of diffuse optical spectroscopic imaging for monitoring the effects of chemotherapy on cancer cells. The device must be able to simultaneously create six frequency sweeps that will modulate external laser drivers through user specified frequency ranges between 50 MHz and 400 MHz. Secondly, the dSAU must also be able to measure two waveforms, one from the aforementioned output and the other received from an external amplified photodiode that will measure the light scattered off the tissue from the modulated laser at a point. Furthermore, the Analyzer must communicate this waveform information to a PC running custom software for recording and visualizing the data. This software must also be able to set frequency sweeps and otherwise control the Analyzer. In order to meet these goals we designed custom printed circuit board(s) with six direct digital synthesizer chips for producing the output waveforms, a two channel 14 bit 250MSPS ADC for measuring the inputs and a Zynq SOC (ARM + Artix-7) with custom firmware and running Linux for controlling these devices and communicating with the PC. We also developed custom PC software written in Visual C++ 2010 and designed to work on Windows 7. All communications use 1000Mbps Ethernet over copper and are platform agnostic.

This project was carried out as a part of an ECE Senior Design Project for the class of 2014.

Revision A

Above is a block diagram of Revision A Analyzer as implemented and finished in May 2014. From organizational standpoint our team was divided into three major groups: hardware development, software development and firmware development. This is important to note throughout the report. While the boundaries of the hardware team are pretty clear the firmware and software groups do have a much fuzzier boundary. We will define firmware as any binary, FPGA bitstream, or related work, which runs on, or configures, the MicroZed?. The software on the other hand will be anything which runs on the computer. The distinction here is that the firmware, can be changed, but shouldn’t (thus the term "firm") and the software is simply an interface for talking for our final hardware solution and could be re-implemented without needing to redesign the hardware.

Our development environments are varied, but can be summarized as following:

- Hardware: Altium Summer 2009 through a BU license. Further details are discussed in the Hardware Report.pdf

- Software: Visual Studio 2010 using Visual C++, compatible with Visual Studio Express C++, further described in the Software Report.pdf

- Firmware: Xilinx Vivado 14.3 and Xilinx ARM GCC cross-compiler, which is described in the Firmware Report.pdf

Specifications

| Parameter | Specification |

| Frequency Synthesis Frequency Range | 0-400 MHz |

| Maximum Number of Daughterboards | 6 |

| DDS Input Clock | 25 MHz (external clock support included) |

| Number of ADC Channels | 2 |

| ADC Bits | 14 2's Complement Signed |

| ADC Sampling Rate | 250 MSPS (external clock support included) |

| Noise Floor (Full Scale Referenced) | -100 dB |

| Motherboard Average Operating Current | 0.885 A @ 5 V |

| Freq. Synth Daughterboard Average Operating Current | 0.3 A @ 5 V |

| ADC Input Impedance | 50 Ohms |

| FPGA to ARM CDMA Throughput | 3 Gbps |

| Ethernet Transmission Throughput | 170 Mbps |

| Firmware Swep Throughput | 1 Gbps |

| Motherboard Dimensions | 9.475" x 6.4" |

| Freq. Synth. Daughterboard Dimensions | 2.5" x 3" |

| Full Assembly Dimensions (no box or standoffs) | 9.475" x 6.4" x 2.6" |

Hardware

Motherboard

- Altium Project (zip)

- Schematic (pdf)

- PCB

- Gerber Files (zip)

- Layout (pdf)

- Roblyer_dDOS_Undersampling_dSAU_MotherboardRevA_PCBNotes

- Bill of Materials (csv, xls)

- Important Datasheets

Frequency Synthesis Daughterboard

- Altium Project (zip)

- Schematic (pdf)

- PCB

- Gerber Files (zip)

- Layout (pdf)

- Roblyer_dDOS_Undersampling_dSAU_DaughterboardRevA_PCBNotes

- Bill of Materials (csv, xls)

- Important Datasheets

Firmware

Software

Windows Build Environment

In order to compile this Client and GUI portions of the software Visual Studio 2010 with Service Pack 1 must be installed. This program can be downloaded through the MDSN website. If Service Pack 1 is not installed there will be issues when trying to build the project. Visual Studio Express C++ 2010 will work and is free for evaluation use; however Service Pack 1 must still be installed.

There are two external libraries used: tinyxml2 (v2.1.0) and ZedGraph (2012-09-19)

To compile the GUI and Client code, the user must download the code. Once the code is downloaded the user should open Visual Studio and select “Open Project”. The user should then find the location where they saved the project and click on the SeniorDesign_1.sln file.

In order to have everything compile correctly there are a few lines of code that must be changed. For the profile name functionality of the GUI to be correct the user needs to change the path to the file that the profile name .xml file is being saved. There are two different locations where this file path needs to be changed. The file path is defined as XMLPATH at the beginning of the header files in Form1.h and ProfileNameWindow?.h. These file paths will only need to be changed if the computer that the GUI is being used on changes. Additionally, the code assumes that the server has an IP address of “192.168.1.10” however if this is not the case it must be changed. This information can be changed in the Form1.h header file. The IP address is defined as IPADDRESS at the top of the header file.

After these file paths have to been changed to appropriate locations and the correct IP address is entered, the code can then be built, compiled and run using Visual Studio 2010 Service Pack 1. Note that after the project is compiled with the appropriate paths and IP address, the .exe file that is located in the Debug folder of the project can be run on its own from a different location without having to open visual studio. However, if the user would like to run it from the Desktop, for example, then the user must also copy and paste the appropriate .dll files to the desktop as well (ClientDLL.dll and ZedGraph?.dll). The ClientDLL.dll is created in the debug folder of the SeniorDesign1 project directory.

Reports and Other Resources

Developers

Current Developers

- Dan Gastler, Primary Maintainer and Developer

- Fei Teng, Research Assistant in Darren's Lab

- Eric Hazen, Overseer

Senior Design Project Team

If the original team is to be contacted please contact the new maintainers first. Eric Hazen or Dan Gastler can redirect questions as needed.

- Christopher Woodall (chris.j.woodall <at> gmail.com), Motherboard PCB Designer & Primary Support Contact

- Thomas Nadovich, Frequency Synthesis PCB Designer

- Benjamin Havey, microZed-Zynq Firmware and Software Developer

- Caroline Ekchian, PC Side Frontend Developer

- Andy Mo, Server-Client Communications Developer

This Senior Design Team also won a Design Excellence Award at ECE Day 2014